# 第4章 論理回路

## 4.1 半導体

半導体の電気的な性質は、電気をよく通す導体と電気を通さない絶縁体の中間に位置します。主な成分はシリコン(Si)やゲルマニウム(Ge)で、リン(P)やヒ素(As)を少量混ぜたN形半導体と、ホウ素(B)やインジウム(In)を少量混ぜたP形半導体があります(シリコンに対して1000万分の1の割合)。以後、シリコンを主成分とし、リンを含んだN形半導体とホウ素を含んだP形半導体について話を進めていきます。

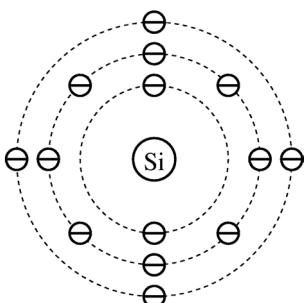

図 4.1: シリコンの原子構造

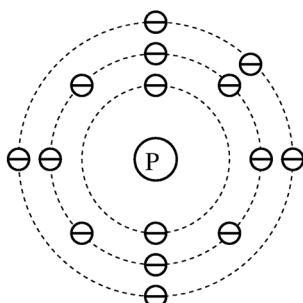

図 4.2: リンの原子構造

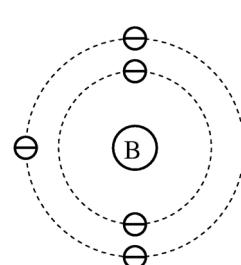

図 4.3: ホウ素の原子構造

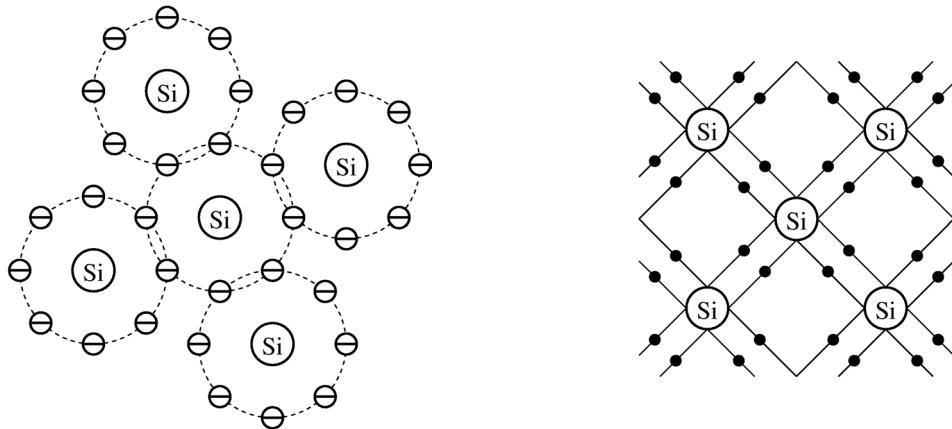

高校の化学で習ったように、各原子は内側からK殻・L殻・M殻といった殻があり、K殻では2個・L殻では8個・M殻では8個の電子が存在することによって安定状態になることが知られています。従って、シリコン・リン・ホウ素の各原子の原子構造は上図のようになっていています。また、シリコンは、図4.4のように隣り合う4つの原子からそれぞれ1個の電子を共有して、電気的に安定した状態になります。このような結合を共有結合と呼びます。

図 4.4: シリコンの共有結合

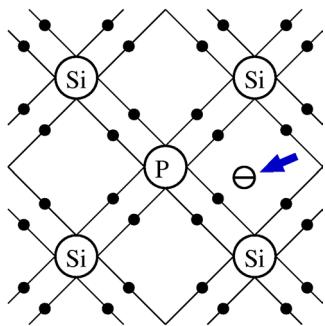

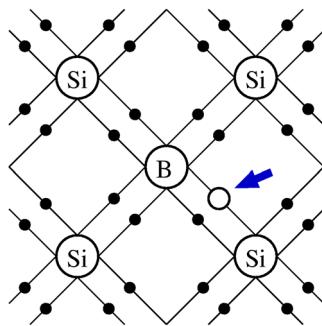

N形半導体やP形半導体は、シリコンに少量のリンやホウ素を混ぜて、電気的に不安定な状態を作ります。N形半導体では、図4.5のようにリンの最外殻(N殻)の5つの電子のうち4つは共有結合に使われ、矢印で示した1個の電子が余った状態になります。逆に、P形半導体では、図4.6のようにホウ素の最外殻(M殻)の3つの電子は共有結合を行いますが、電子が1個足りないため矢印で示したホールと呼ばれる状態になります。

図 4.5: N形半導体

図 4.6: P形半導体

本題に入りますが、上記で説明したN形半導体とP形半導体を組み合わせることで、論理回路の元となる電子部品が作られます。代表的なものにはダイオードとトランジスタがあります。

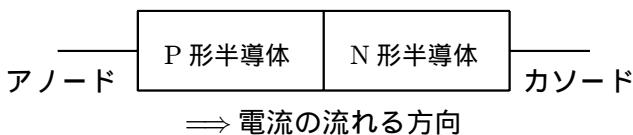

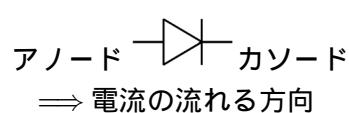

**ダイオード** ダイオードは、図4.7のようにN形半導体とP形半導体をPN接合することで、P形半導体からN形半導体への一方向しか電流を流さないという性質を持ちます。なお、P形半導体の端子とN形半導体の端子をそれぞれアノード及びカソードと呼び、ダイオードの回路記号は図4.8によって表示します。

図 4.7: ダイオードの接合図

図 4.8: ダイオードの回路記号

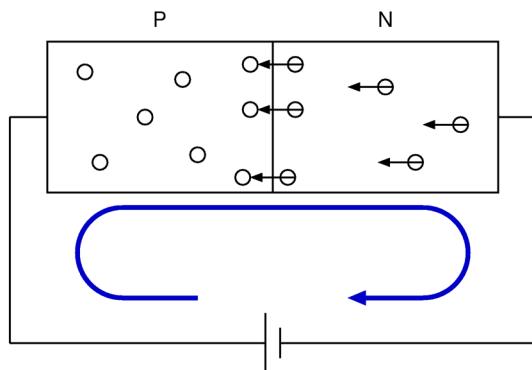

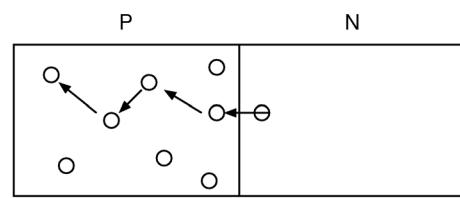

ダイオードの働きについて詳しく見てみましょう。先ほど述べたように、ダイオードは、一定方向のみ電流を流す性質を持っていますが、図 4.9 のように電流が流れる場合を順方向バイアスと呼び、図 4.11 のように電流が流れない場合を逆方向バイアスと呼びます。順方向バイアスでは、電子はカソードからアノードへ流れようとするため、PN 接合面では N 形半導体の余った電子が P 形半導体のホールへ移動し、N 形半導体から P 形半導体へ電子が流れます。すなわち、P 形半導体に入った電子は図 4.10 のようにホールを動きながらアノードへ達し正極へ流れて行き、カソードでは負極から N 形半導体へ次々に電子を供給するので、回路に電流が流れます。

図 4.9: 順方向バイアス

図 4.10: 電子の動き

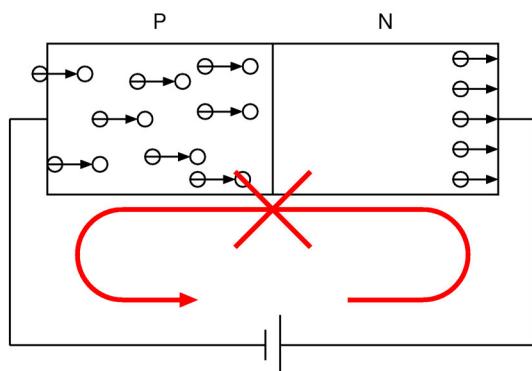

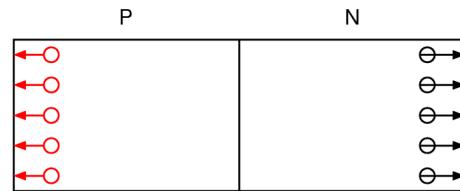

逆に、逆方向バイアスでは、電子はアノードからカソードへ流れようとするため、N 形半導体の余った電子は正極へ流れ、P 形半導体では負極から供給された電子によってホールを埋めてしまいます。そのため、両方の半導体が電気的に安定した状態となり、PN 接合面で電子のやり取りがなくなり、回路に電流が流れなくなります。なお、図 4.12 のように、逆方向バイアスではホールと電子が両極に移動すると解説されている場合もあります。これは、電子がホールを埋めるとき、あたかもホールが流れているように見えるためです。

図 4.11: 逆方向バイアス

図 4.12: 電子とホール

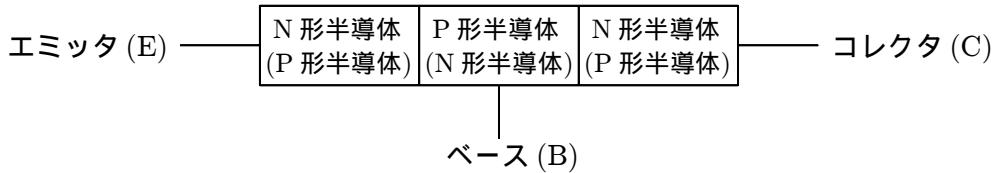

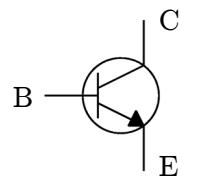

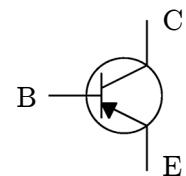

**トランジスタ** トランジスタは、N形半導体とP形半導体を図4.13のようにNPN接合またはPNP接合したもので、各端子をエミッタ・コレクタ・ベースと呼び、ベースに(入力)電流を流すことでコレクタとエミッタに増幅した(出力)電流を流します。図4.14はNPN形トランジスタの回路記号を表し、図4.15はPNP形トランジスタの回路記号を表します。

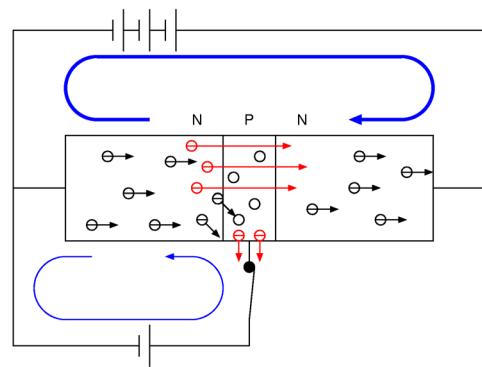

図4.13: トランジスタの接合図

図4.14: NPN形トランジスタの回路記号

図4.15: PNP形トランジスタの回路記号

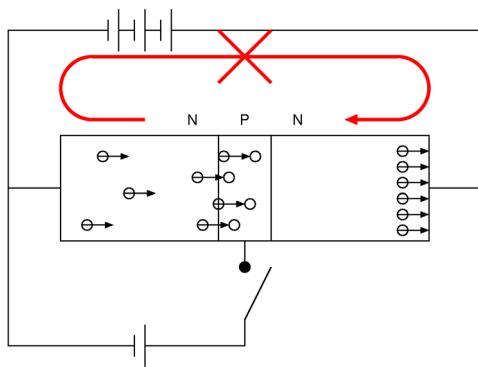

NPN形トランジスタの働きについて詳しく見ていきましょう。図4.16のようにベースに電流が流れていなければ、回路右側のPN接合部がダイオードの逆方向バイアスと同じようになります。逆に、図4.17のようにベースに電流が流れている場合は、回路左側のNP接続部がダイオードの順方向バイアスと同じようになります。エミッタからコレクタへ電流が流れようになります。このとき、コレクタ—ベース間よりコレクタ—エミッタ間の電圧が高いため、ほとんどの電子はP形半導体を突き抜けてエミッタに流れてしまいます。なお、エミッタからコレクタへ流れる電流の量はベースへ流す電流に対応して変化しますが、これは、ベースを水道の蛇口に例えると、電流の流量は水量に例えることができます。

図4.16: ベース電流を流さない場合

図4.17: ベース電流を流した場合

問題1 電子とホールに注目して、PNP形トランジスタの働きを解説しなさい。

## 4.2 論理素子

論理素子は論理演算を回路で実現したもので、真理値 1 および 0 に対応する 2 つの状態を安定して表せる論理素子が必要となります。現代のコンピュータは半導体によって実現されていますが、半導体が発明されるまでは電磁リレーや真空管を使用していました。そのような背景から、構成される論理素子の違いによってコンピュータの世代が特徴づけられていて、第 1 世代は真空管、第 2 世代は個別の半導体トランジスタ、第 3 世代は半導体の集積回路 (IC:Integrated Circuit)、第 4 世代は集積度の高い大規模集積回路 (LSI:Large Scale Integrated circuit) に分類されます。現在は第 4 世代にあたります。

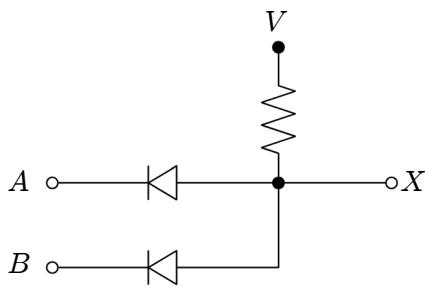

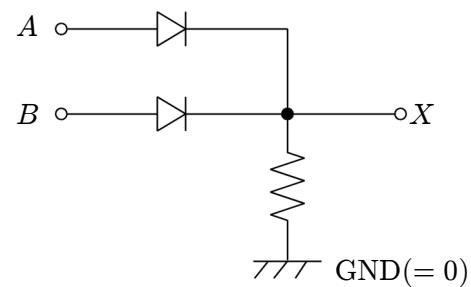

半導体による論理素子では、電圧の高い状態  $V$  と低い状態 0 を真理値の 1 と 0 に対応させて考えますが、電圧の高い状態を 1・低い状態を 0 に対応させた正論理 (positive logic) と、高い状態を 0・低い状態を 1 に対応させた負論理 (negative logic) があります。このテキストでは全て正論理で解説します。従って、基本的な論理演算である AND 回路と OR 回路は、2 個のダイオードを使って図 4.18 と図 4.19 のように構成することができます。なお、図中の  $A$  と  $B$  は入力端子、 $X$  は出力端子を表します。

図 4.18: AND 回路

図 4.19: OR 回路

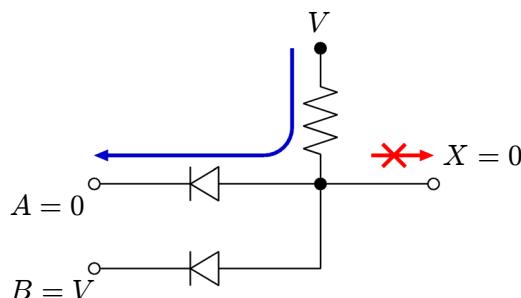

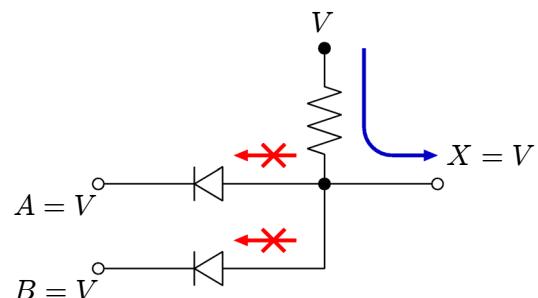

図 4.18 の AND 回路について動作を詳しく見てみましょう。図 4.20 のように、入力端子に低い電圧の状態を含む場合、電流は電圧の低い入力端子に流れ、出力端子の電圧は 0 になります。逆に、図 4.21 の場合、ダイオードの両端の電圧が等しいため電流は出力端子に流れ、出力端子の電圧は  $V$  になります。従って、この回路は論理積の働きをすることがわかります。

図 4.20:  $A = 0$  かつ  $B = V$  の場合図 4.21:  $A = V$  かつ  $B = V$  の場合

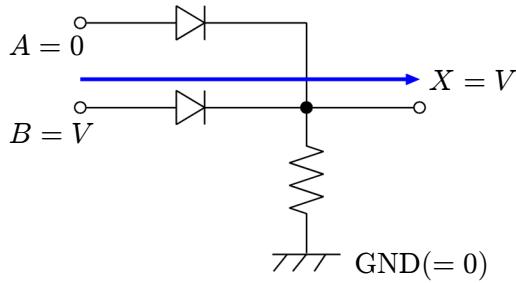

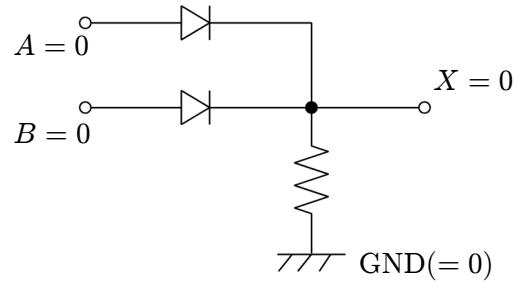

同様に、図 4.19 の OR 回路は論理和の働きをすることがわかります。

図 4.22:  $A = 0$  かつ  $B = V$  の場合

図 4.23:  $A = 0$  かつ  $B = 0$  の場合

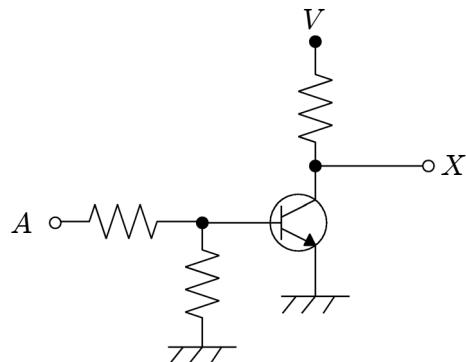

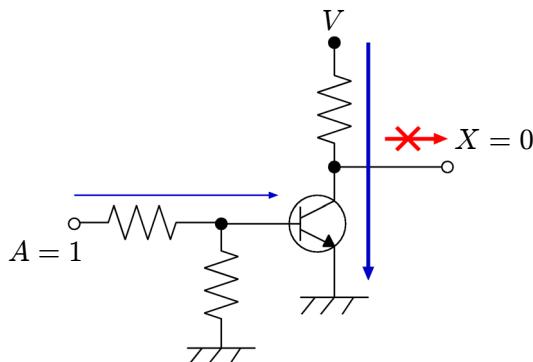

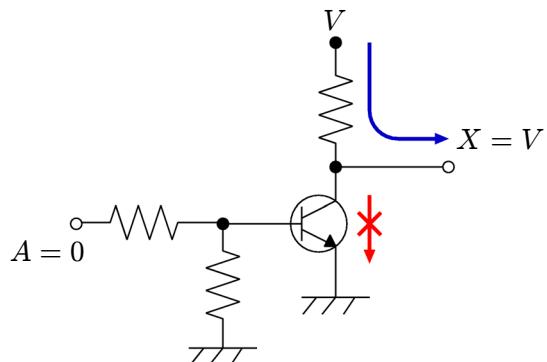

NOT 回路については、トランジスタを使って図 4.24 のように構成することができます。入力端子の電圧が  $V$  の場合、図 4.25 のようにトランジスタのベースに電流が流れるため、図の電圧  $V$  によって流れる電流は電圧の低い GND に流れてしまい、出力端子の電圧は 0 となります。逆に、入力端子の電圧が 0 の場合、図 4.26 のようにトランジスタのベースに電流が流れないため、図の電圧  $V$  によって流れる電流は出力端子に流れ、出力端子の電圧は  $V$  となります。従って、この回路も否定の働きをすることがわかります。

図 4.24: NOT 回路

図 4.25:  $A = V$  の場合

図 4.26:  $A = 0$  の場合

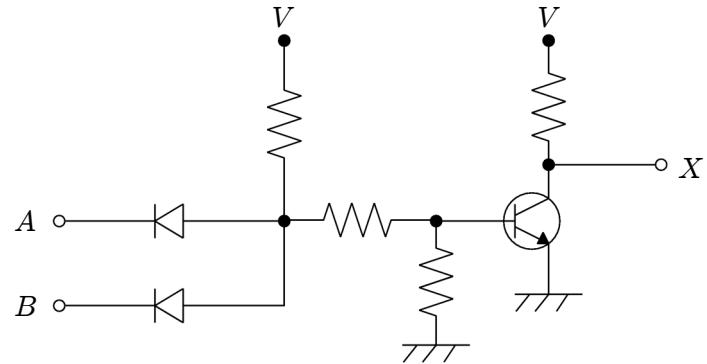

以上のことより、3.4 節で述べた 1 つの演算で最小万能演算系となる否定積の論理素子である NAND 回路は、図 4.27 のように構成することができます。

図 4.27: NAND 回路

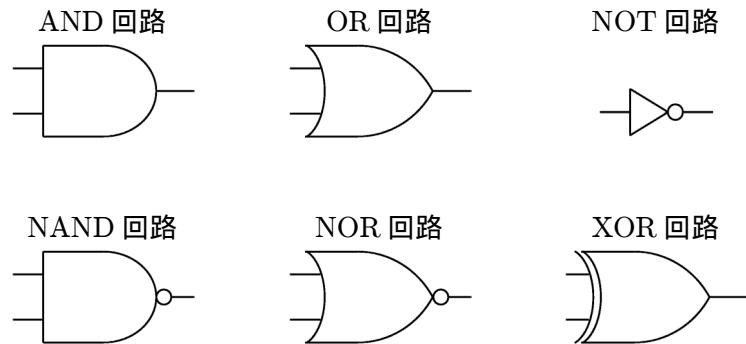

論理回路を電子部品で書き表すと煩雑となりますので、論理素子を簡略化した [MIL 記号](#)を導入しましょう。MIL 記号は、アメリカ合衆国の軍隊で使われていたもので、砲弾の弾道を計算するためにコンピュータが発達してきたという歴史的背景から、現在でもこの記号が使われます。図 4.28 は MIL 記号の代表的なもので、左側が入力、右側が出力となります。

図 4.28: MIL 記号

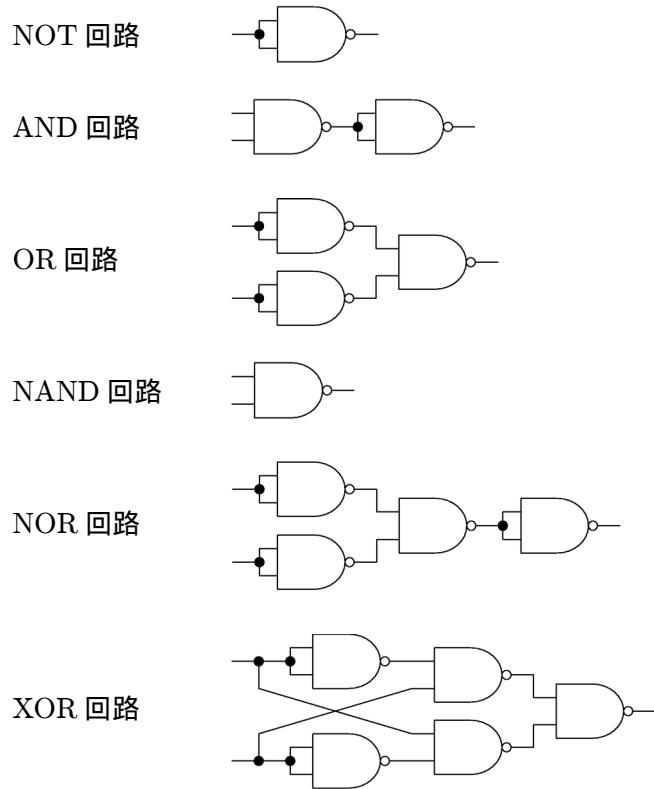

3.4 節で述べたように、否定論理和によって全ての論理関数を表すことができますので、図 4.29 のように MIL 記号の NAND 回路を用いて基本回路を構成することができます (p.31 の表 3.6 参照)。

図 4.29: NAND 回路による基本回路の構成

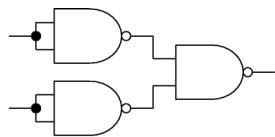

**例題 1** MIL 記号の NOT 回路と OR 回路を使って NOR 回路を作りなさい。

解答例  $A \downarrow B = \overline{A + B}$  であるから、

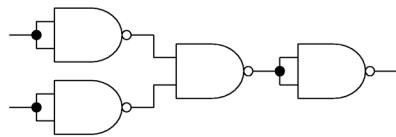

**例題 2** MIL 記号の NOT 回路と OR 回路を使って NAND 回路を作りなさい。

解答例  $A | B = \overline{A \cdot B} = \overline{A} + \overline{B}$  であるから

問題 1 OR 回路の動作について詳しく述べなさい。

問題 2 負論理では、図 4.18 の回路は OR 回路に、図 4.19 の回路は AND 回路になります。理由を述べなさい。

問題 3 MIL 記号の NOR 回路のみを使って基本回路を構成しなさい。

問題 4 次の論理回路で表される論理関数を求めなさい。

(1)

(2)

問題 5 MIL 記号の NAND 回路のみを使って論理式  $(A \cdot B + C \cdot D) \cdot \overline{C}$  を実現する回路を作りなさい。